「イコライザって、ほんとに波形をキレイにできるの?」そう思ったことはありませんか?

この記事では、前回作成した「CTLEモデル ~AC解析~」を使って、「イコライザ」の波形改善効果をLTSpice上で実際に確認していきます。

結果を先にちょっとだけ話すと、つぶれたアイパターンが「イコライザ」のおかげでなんと見違えるほどキレイになったんです!

思わず「おおっ」と声が出るほど、その効果にはほんとおどろきました。

>>Step6:アイパターンを比較する(イコライザ有り vs 無し)

信号波形をキレイにしてくれるこの「イコライザ」は、ギガビットの高速デジタル伝送には必要不可欠です。オーディオ分野でも音を良くするのにイコライザが使われてますが、電気の世界でも、おなじくらい大事な技術なんです。

この記事では、初めての方でもわかりやすいように、LTSpiceの回路図作成からシミュレーションの実行まで、一つひとつ手順を画像と一緒にくわしく説明しています。

そして後半部分では、LTSpice上でイコライザの信号改善効果を実際に目で見て確認していきます。イコライザを通過した前と後のアイパターンを比較することで、その変化を体験できると思います。

さらに、この記事の中で使っているサンプル回路(LTSpice)をダウンロードできます。興味がわいたらぜひ試してみてください。

LTSpiceでアイパターンを表示する方法はかんたんです。

回路図に「.OPTIONS BAUDRATE」を書けばOKです!

もくじ

作成する回路図とシミュレーション画面

LTSpiceの動作環境

- LTSpice XVII

- Windows10 (64bit)

作成する回路図(アイパターン表示)

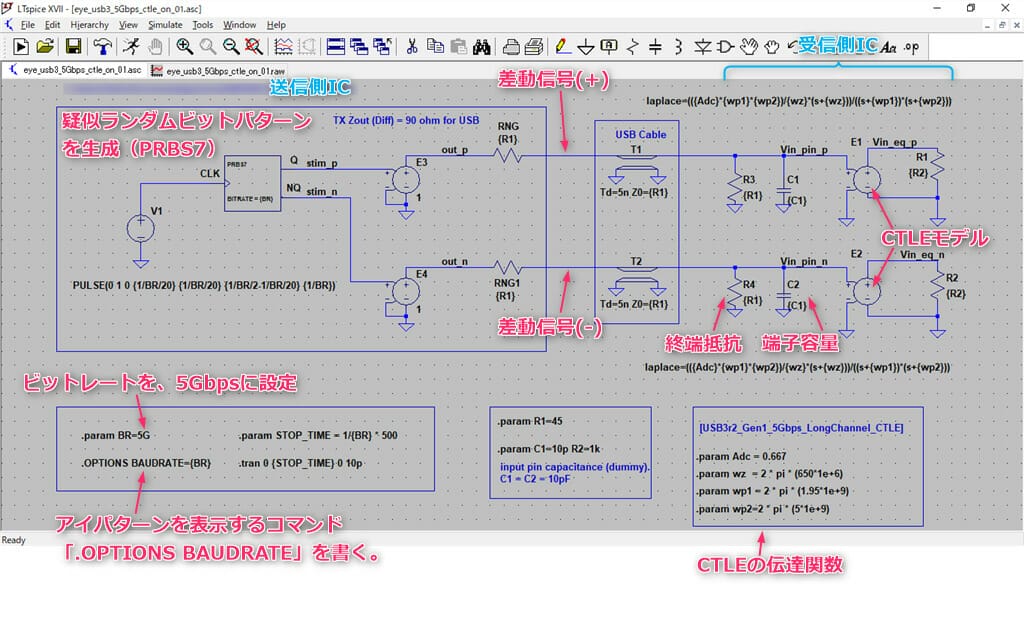

↓ 下図が、USB3.2(5Gbps)の差動信号のアイパターン(Eye Diagram)を表示する回路です。この回路図を作っていきます。

(USB Super Speedの場合、本来は、送信IC側に「ACカップリング・コンデンサ」の挿入が必要ですが、この回路では省略してます。)

LTSpiceでアイパターンを表示するには、回路図の左下にある「.OPTIONS BAUDRATE ={BR} 」を書けばOKです!

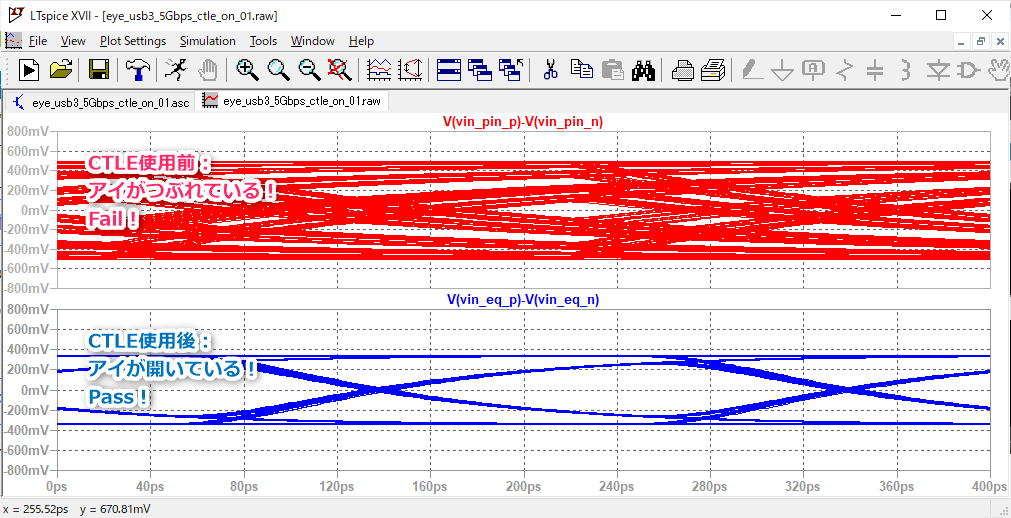

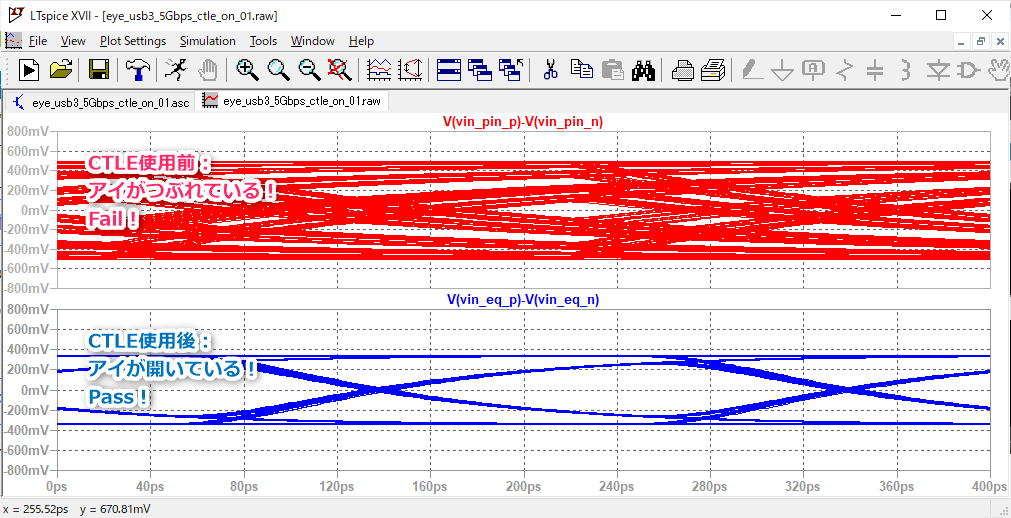

アイパターン表示画面(CTLE使用前/後)

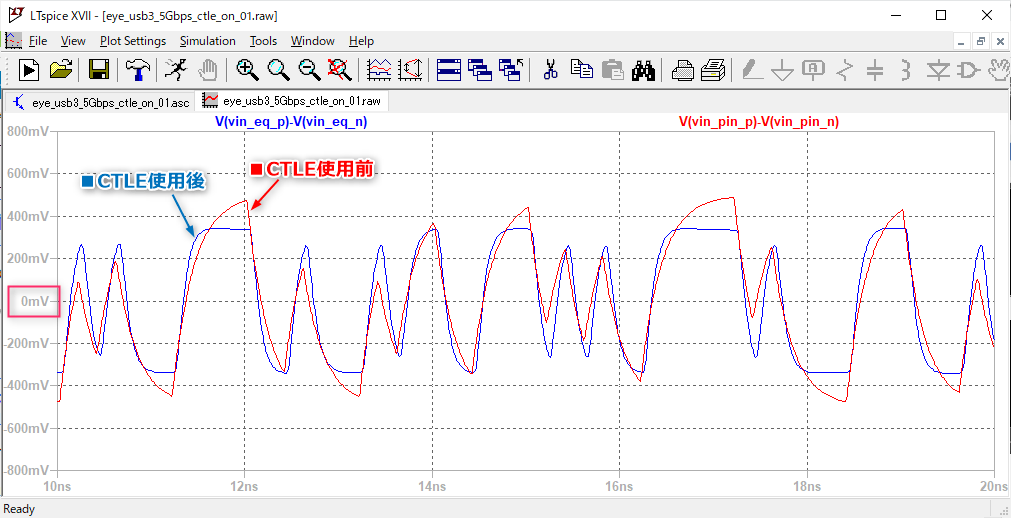

↓ 下図は、CTLE使用前/後のアイパターン比較です。(赤:CTLE使用前、青:CTLE使用後)

イコライザを使う方(下段:青)が、アイがキレイに開いてる!

波形シミュレーション画面(CTLE使用前/後)

↓ 下図は、CTLE使用前/後の波形比較です。(赤:CTLE使用前、青:CTLE使用後)

アイパターンのような”重ね書き”ではなく、時間的に連続した波形の一部分を表示したものです。

イコライザあり・なしで波形比較すると、イコライザーの効果が良くわかる!

ではこれから、回路図の作成方法と、シミュレーションの実行方法を説明していきます。

CTLEモデルで、アイパターンを表示してみよう

新しい回路図を作成する

新しい回路図を作成します。

LTSpiceを起動 ⇒ ツールバーの「File」⇒「New Schematic」⇒ 新しい回路図が開きます ⇒ もう一度「File」⇒「Save as」でファイル名をつけて保存します。

ファイルの保存忘れがないように、はじめに保存しておきます。

>>完成成回路図を見ながら、各部品を回路図上に配置して、部品同士をつないでいきます。

「部品」を設定する

部品を設定します。サンプル回路の設定画面を見ながら同じように設定していきます。

PRBS発生器のクロック信号用「電圧源」

「電圧源V1」を”右”クリック ⇒ 設定画面が表示 ⇒ 「PULSE」をチェック ⇒ 下記画面のように入力 ⇒ 「OK」ボタン。

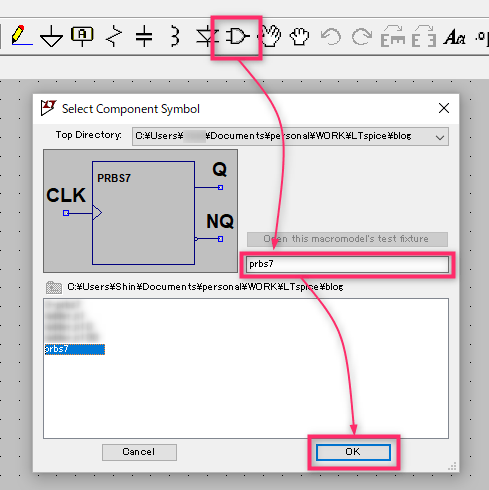

PRBS発生器のシンボルを呼び出す

PRBS7のシンボルを呼び出して、回路図に配置します。

ツールバーの「Component」アイコン ⇒ prbs7 を入力 ⇒ OKボタン ⇒ 回路図上で左クリックすると配置されます。

送信IC用「電圧制御電圧源」

送信ICの信号出力を模擬するために、「電圧制御電圧源」を使います。

「電圧制御電圧源」E3、E4を”右”クリック ⇒ 設定画面が表示 ⇒ Value欄に入力 ⇒ 「OK」ボタン。

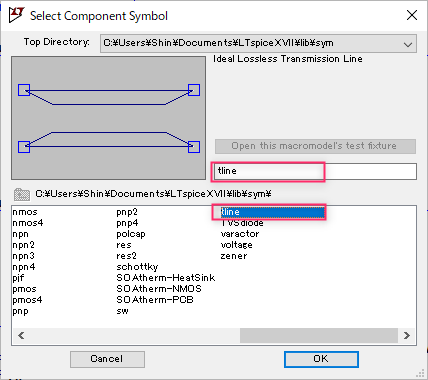

USBケーブル用「tllne(無損失伝送路モデル)」

本サンプル回路図では、USBケーブルを、無損失伝送路モデル「tline」で代用してます。

ツールバーの「Component」アイコン ⇒ 「tline」を入力 ⇒ OKボタン ⇒ 回路図上で左クリックすると配置されます。

つづいて、配置した「tline」を ”右”クリック ⇒ 設定画面が表示 ⇒ Value欄に以下を入力 ⇒ 「OK」ボタン。

ビットレートが 5Gbpsの高速デジタル伝送になると、基板業界では「IBIS-AMIモデル」を使ってシミュレーションするのが一般的。ただ、シミュレータソフトがめちゃ高い!

LTSpiceは無料!

IBISやSパラメータを扱えないけど、「こうやればできるかな~?」っていろいろ考えるのが楽しいところ!

イコライザCTLEモデル用「電圧制御電源」

CTLEモデルの作り方は、↓以下の前回記事に説明があります。

>>【LTSpice】イコライザ(CTLE)を、Laplace関数で作ってみよう ~AC解析~

「電圧制御電圧源」E1、E2を”右”クリック ⇒ 設定画面が表示 ⇒ Value欄に、以下の式を入力 ⇒ 「OK」ボタン。

アイパターンを表示させるための設定

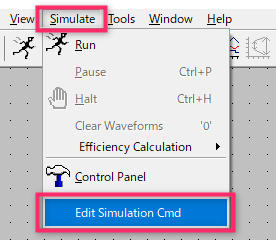

Transient解析を設定する

Simulate ⇒ Edit Simulation Command をクリック。

「Edit Simulation Command」画面が表示されるので、Transientタブ ⇒ 下記画面のように入力します。

入力が終わると、Transient解析のSpiceコマンド「.tran 0 {STOP_TIME} 0 10p」が自動的に設定されます。

ツールバーの「File」⇒ 「Save」で上書き保存します。

以上で、回路図が完成です!

Transient解析を実行する

シミュレーションを実行して、アイパターンを表示してみよう。

メニューバーの「RUN」(人が走っているアイコン)をクリック ⇒ シミュレーションが実行されます。

シミュレーション結果を確認する

シミュレーションが完了したら、 回路図の配線をクリックして、その配線のアイパターンをグラフに表示させます。

アイパターンが表示されない場合は?

- 回路図にSpiceコマンド「.OPTIONS BAUDRATE={BR}」を書いてますか?

もしない場合は、書くこと。 - 「.OPTIONS BAUDRATE={BR}」を”右”クリック ⇒ 「SPCIE directive」にチェックが入ってますか?

もし「Comment」の方にチェックが入っている場合は、「SPCIE directive」へ変更すること。

つづいて、グラフ上に表示させた信号名を、プラス信号からマイナス信号を引き算するように変更します。

グラフ上の信号名を””クリック ⇒ 信号名を、

(例) V(vin_eq_p) ⇒ V(vin_eq_p)-V(vin_eq_n) へ変更。

アイパターンを比較する(イコライザ有り vs 無し)

最後は見やすいように、信号の色、タテ・ヨコ軸の目盛を調整すると、下のアイパターンのようになります。

上側のアイパターン(赤)はつぶれてますが、下側のイコライザを通ったアイパターン(青)はキレイに開いてます。これはスゴイ!

イコライザあり・なしで波形比較すると、イコライザーの効果が良くわかる!

以上で、回路図作成〜シミュレーションまで実行できました。

参考文献

Universal Serial Bus 3.2 Specification >>USB-IF公式サイト

サンプル回路をダウンロードする

この記事のサンプル回路(LTSpice)をダウンロードできます。もしよければお試しください。

無料の電子回路シミュレータ「LTSpice」のオススメ本を紹介します。

「LTSpiceをマスターしたい!」という方に、初心者向けのオススメ本の紹介です。もし興味があれば以下リンクもチェックしてみてください。

>> 初心者でもLTSpiceを使いこなす!使い方の基本とテクニックを学べるおすすめ本3冊+動画

-

-

初心者でもLTSpiceを使いこなす!使い方の基本とテクニックを学べるおすすめ本3冊+動画

続きを見る

まとめ:【LTSpice】イコライザの効果を確認しよう

この記事では、前回作成した「CTLEモデル ~AC解析~」を使って、イコライザの波形改善効果の違いをアイパターンで比較してみました。

「イコライザ」を使うと、つぶれたアイパターンがキレイになるのはホントおどろきですよね!

イコライザは、これからのギガビットの高速デジタル伝送では欠かせない技術。

「ギガビットの高速信号の回路設計についてもっと知りたい!」って方にオススメの本があります。この本を読めば今よりもっと回路設計者としての知見が深くなるはずです。以下のリンクもぜひご覧ください。

>>【高速デジタル信号】回路設計・基板パターン設計の第一歩!初心者にピッタリの本3冊

-

-

【高速デジタル信号】回路設計・基板パターン設計の第一歩!初心者にピッタリの本3冊

続きを見る