SerDesで使われている「イコライザ」について知りたい。

- イコライザを使うと波形がキレイになるってホント?

イコライザを使う前と後で、波形がどう変わるか見てみたい。 - イコライザにはどんな種類があるの?

- それぞれの特長も知りたい。

こんな疑問にお答えします。

この記事の内容

- イコライザの波形改善効果を検証【LTSpiceでシミュレーションしてみた】

- イコライザの種類【代表例を紹介】

- イコライザの特長【FFE、CTLE、DFE】

この記事では、高速シリアルインターフェース「SerDes」で使われている「イコライザ」の機能やその波形改善効果について紹介しています。

転送スピードが速くなるほど、プリント基板上を伝わる信号波形はどんどんなまっていきます。そして、信号波形が劣化すると送信回路と受信回路で正しい信号の受け渡しができず、結果、システムが誤動作する場合があります。

ギガビット(Gbps)の高速デジタル伝送では、上記のような波形トラブルの解決策として、「イコライザ」という補正回路で波形をキレイにする技術を使っています。

高速デジタル伝送回路を設計するときには、おさえておきたい必須の知識です。わかりやすく説明していますのでぜひお読みください。

もくじ

『イコライザ』の改善効果を検証【LTSpiceでシミュレーションしてみた】

「イコライザ」とは、減衰した信号波形を補正して、閉じたアイパターンの開口を大きくするための技術の一つです。

以下は、イコライザ(CTLE)による波形補償 あり/なしの、アイパターンの比較結果です(LTSpiceでシミュレーション)。

イコライザ:なし

イコライザ:あり

すごい! イコライザを使うとアイがこんなに開く!

ご覧のように、イコライザ”あり”にすると、閉じていたアイパターンが大きく開いていますね。

ギガビットの高速信号がプリント基板上を通過すると、波形がなまってアイパターンが閉じてしまう場合があります。

劣化した信号波形を「イコライザ」と呼ばれる回路技術で補償することにより、アイパターンが「ぱかっ」と開くようになります。

-

-

【LTSpice】つぶれたアイパターンがキレイに改善?「イコライザ」の効果を確認してみよう!

続きを見る

SerDesでよく使われる波形補償回路【代表例】

波形補償回路にはいくつか種類があります。

下表は、SerDes ICが採用している代表的な波形補償回路です。

| 略語 | 名称 | 方式 | 説明 |

| FFE | Feed Forward Equalizer フィード・フォワード・イコライザー | デジタル | ・送信回路(トランスミッタ)で使用。 ・FIR(有限インパルス応答)フィルタで実現、 デエンファシスや、プリエンファシスの機能を包含。 |

| CTLE | Continuous Time Linear Equalizer 連続時間線形イコライザ | アナログ | ・受信回路(レシーバ)で使用。 ・ハイパスフィルタと、ローパスフィルタを組み合わせて実現。 |

| DFE | Decision Feedback Equalizer 判定帰還型イコライザ | デジタル | ・受信回路(レシーバ)で使用。 ・CTLEの後段に実装。 ・シンボル間干渉(ISI:Inter Symbol Interference)ジッターを低減。 |

回路設計現場でのことばの使いわけについての補足です(わたしの経験上)。

送信回路(トランスミッタ)では「FFE」を使用し、一方、受信回路(レシーバ)では「CTLE」と「DFE」を使うことが多いようです。

>> 高速シリアルインターフェース「SerDes」とは? ~回路構成・高速化技術・イコライザなど~

送信回路(トランスミッタ)で使われる波形補償回路

プリエンファシス(Pre-Emphasis)

「プリエンファシス」や「ディエンファシス」は、送信信号に対して波形改善する技術です。

基板上で損失する高周波成分(信号の立ち上り・立ち下り部分の振幅)を送信回路側で、あらかじめ大きくしてから送信する方式です。

回路的には、デジタルフィルタ(FIRフィルタ)で構成されています。

FIR:Finite Impulse Response(有限インパルス応答フィルタ)

立ち上り・立ち下りエッジの部分は高い周波数成分を持つので、基板パターンの損失で波形がなまってしまいます。

この改善策として、あらかじめこのエッジ部分のスルーレートを上げて振幅を大きくして送信することで、受信端のアイパターンが開くようにします。

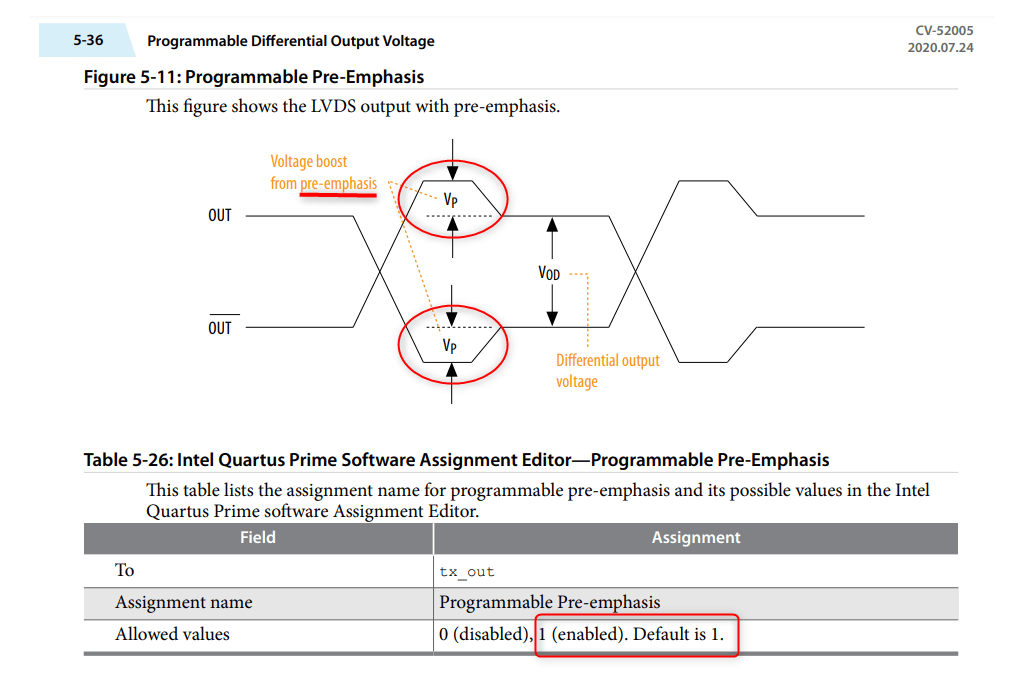

↓ 下図は、Intel社FPGAの出力信号波形の例です。

赤丸の箇所に注目してください。出力波形の立ち上り時と立ち下り時に、電圧振幅が持ち上がってますね! 基板上で波形がなまってしまう分を出力側で持ち上げることでおぎなっています。

上の表の赤ワクを見てください。Pre-emphasis(プリエンファシス)が、初期設定で 1 (enabled)(有効)になっています。

もし、0(disable)にしてプリエンファシス未使用でも受信端側の実測波形がキレイであれば、disableにした方が、ノイズ発生のリスクが減り、消費電力も小さくなります。

プリエンファシスを使うと、EMI(ノイズ)が大きくなる場合があります!

使うICのプリエンファシス機能の初期設定がどうなっているか(有効 or 無効)? データシートを確認しておきましょう。

プリエンファシスを使うと、波形の立ち上りが急峻な分、どうしてもEMI(ノイズ)が増えてしまう心配がありますよね?

以下、プリエンファシスを使うか、使わないか? ざっくりとした考え方です。

- 送信ICと受信ICを、同じ基板上に実装し、基板パターンで接続する場合: プリエンファシスを使わない。

- 送信ICと受信ICを、別々の基板上に実装し、ケーブル経由で接続する場合: プリエンファシスを使う。

同じ基板上で、送信ICと受信ICを接続する場合は、プリエンファシスを使わない(disabledにする)方が無難です。

この場合、基板寸法が数10cm程度と考えると、パターンの長さはそれほど長くはないので、プリエンファシスを使って補正するほど、基板パターンの損失はないと思います。

一方、別々の基板同士を、ケーブルで接続する場合は、ケーブルの損失が大きいため、波形が劣化することが想定されます。

この場合は、受信端の波形品質確保の観点から、プリエンファシスの”有効”が必要な場合があります。

プリエンファシスを使うとノイズが大きくなる心配があるのか。

使うかどうかの最終評価は、実機で受信端の波形を見て判断しよう!

ディエンファシス(De-Emphasis)

ディエンファシスは、プリエンファシスとは逆に、信号レベルが変化”しない”部分の振幅を小さくして、相対的に立ち上り・立ち下り部分の振幅を大きくしてから送信する方式です。

ディエンファシスは、USB3.xやPCI Expressで採用されています。

受信回路(レシーバ)で使われる波形補償回路

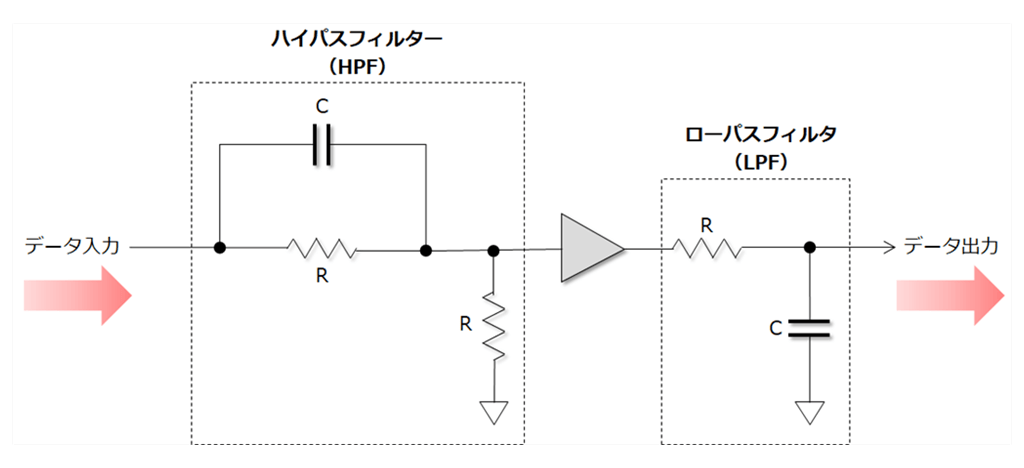

CTLE(Continuous Time Linear Equalizer)

CTLEは、ハイパスフィルタとローパスフィルタで構成されたアナログフィルタ回路です。時間的に連続動作します。

このアナログフィルタは、高周波成分を増幅する特性を持っていて、基板上で損失した高い周波数成分を補償します。

弱点は、「ノイズまで増幅してしまう!」という点です。

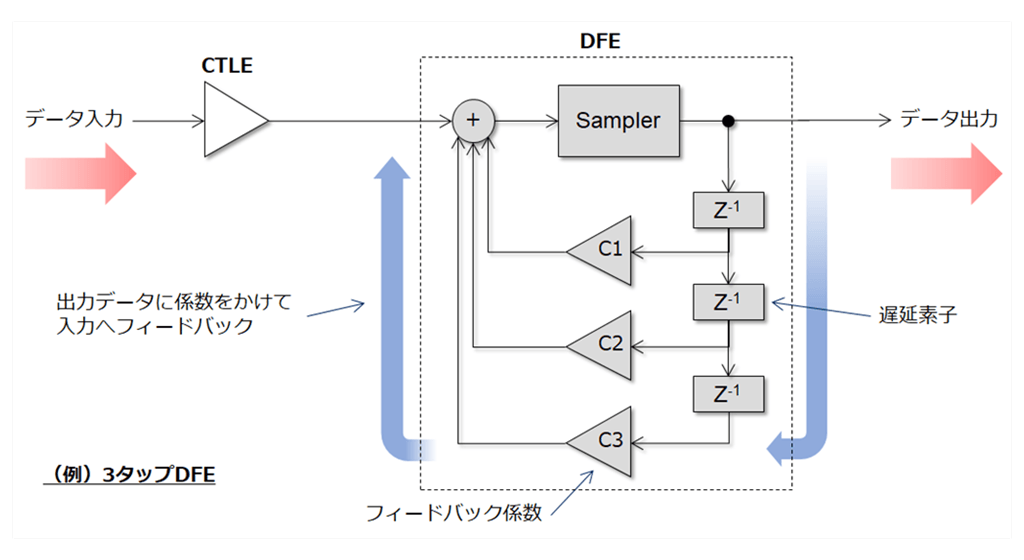

DFE(Decision Feedback Equalizer)

DFEは、CTLEでアイパターンをある程度開かせてから使うため、前段のCTLEと一緒に使われます。

回路的には、DFEはデジタルフィルタ「IIRフィルタ」で構成されています。(CTLEはアナログフィルタ)

IIR:Infinite Impulse Response(無限インパルス応答フィルタ)

DFEは、ノイズ成分を増幅せずにISIを低減できるところがメリットです。データのビットパターンの状態に応じてデジタルフィルタで演算し、アイパターンを開くようにします。

一方、CTLEは、高域成分を増幅するときにノイズ成分も増幅してしまいます。

↓ 下図は、3タップDFEの例です。

信号を遅延する素子と、係数をかける重み付けする回路(タップ)で構成されます。タップの数を増やすことで、受信波形をより細かく補償できるようになります。

まとめ:高速デジタル伝送を実現する、イコライザ技術

この記事では、高速シリアルインターフェース「SerDes」で使われている「イコライザ」の機能やその波形改善効果について紹介しました。

ギガビット(Gbps)の高速デジタル伝送では「イコライザ」という補正回路で波形をキレイにする技術を使っています。

もし実機で波形トラブルなどが起きた場合は、イコライザの設定値を調整することで改善する場合もあります。

以下リンクでは、ギガビットの高速信号の回路設計についてもっと知りたい方にオススメの本を紹介しています。こちらもぜひ読んでみてください。

>>【高速デジタル信号】回路設計・基板パターン設計の第一歩!初心者にピッタリの本3冊

-

-

【高速デジタル信号】回路設計・基板パターン設計の第一歩!初心者にピッタリの本3冊

続きを見る